# **DDR4 SDRAM**

P3AAG2BLF P3AAG3BLF P3AAG4BLF

# Features

- $V_{DD} = V_{DDQ} = 1.2V \pm 60 mV$

- $V_{PP} = 2.5V$ , -125mV, +250mV

- On-die, internal, adjustable V<sub>REFDQ</sub> generation

- 1.2V pseudo open-drain I/O

- $T_C$  maximum up to 95°C

- 64ms, 8192-cycle refresh up to 85°C

- 32ms, 8192-cycle refresh at >85°C to 95°C

- 16 internal banks (x4, x8): 4 groups of 4 banks each

- 8 internal banks (x16): 2 groups of 4 banks each

- 8*n*-bit prefetch architecture

- Programmable data strobe preambles

- Data strobe preamble training

- Command/Address latency (CAL)

- Multipurpose register READ and WRITE capability

- Write leveling

- Self refresh mode

- Low-power auto self refresh (LPASR)

- Temperature controlled refresh (TCR)

- Fine granularity refresh

- Self refresh abort

- Maximum power saving

- Output driver calibration

- Nominal, park, and dynamic on-die termination (ODT)

- Data bus inversion (DBI) for data bus

- Command/Address (CA) parity

- Databus write cyclic redundancy check (CRC)

- Per-DRAM addressability

- Connectivity test

- JEDEC JESD-79-4 compliant

- sPPR and hPPR capability

| Options <sup>1</sup>                                                                                                                                                                                | Marking                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Configuration                                                                                                                                                                                       |                              |

| – 4 Gig x 4                                                                                                                                                                                         | 4G4                          |

| – 2 Gig x 8                                                                                                                                                                                         | 2G8                          |

| – 1 Gig x 16                                                                                                                                                                                        | 1G16                         |

| <ul> <li>Timing - cycle time</li> <li>0.625ns @ CL = 22 (DDR4-3200)</li> <li>0.682ns @ CL = 21 (DDR4-2933)</li> <li>0.750ns @ CL = 19 (DDR4-2666)</li> <li>0.833ns @ CL = 17 (DDR4-2400)</li> </ul> | -GJK<br>-GJY<br>-GJX<br>-GJN |

| <ul> <li>Operating temperature</li> </ul>                                                                                                                                                           |                              |

| – Commercial ( $0^{\circ} \le T_{C} \le 95^{\circ}C$ )                                                                                                                                              | None                         |

| – Industrial (–40° $\leq$ T <sub>C</sub> $\leq$ 95°C)                                                                                                                                               | IT                           |

# Addressing

| Parameter                  | 4096 Meg x 4   | 2048 Meg x 8   | 1024 Meg x 16  |

|----------------------------|----------------|----------------|----------------|

| Number of bank groups      | 4              | 4              | 2              |

| Bank group address         | BG[1:0]        | BG[1:0]        | BGO            |

| Bank count per group       | 4              | 4              | 4              |

| Bank address in bank group | BA[1:0]        | BA[1:0]        | BA[1:0]        |

| Row addressing             | 256K (A[17:0]) | 128K (A[16:0]) | 128K (A[16:0]) |

| Column addressing          | 1K (A[9:0])    | 1K (A[9:0])    | 1K (A[9:0])    |

| Page size <sup>1</sup>     | 512B           | 1KB            | 2КВ            |

Notes: 1. Page size is per bank, calculated as follows:

Page size = 2<sup>COLBITS</sup> × ORG/8, where COLBIT = the number of column address bits and ORG = the number of DQ bits.

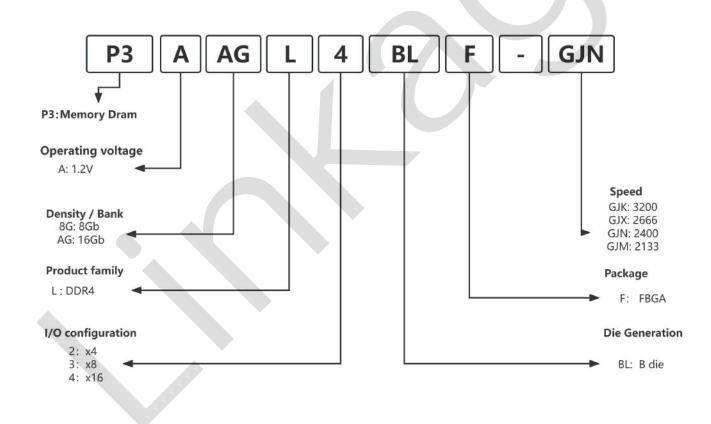

# Figure 1: Order Part Number Example

# **General Notes and Description**

# Description

The DDR4 SDRAM is a high-speed dynamic random-access memory internally configured as an eight-bank DRAM for the x16 configuration and as a 16-bank DRAM for the x4 and x8 configurations. The DDR4 SDRAM uses an 8*n*-prefetch architecture to achieve high-speed operation. The 8*n*-prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins.

A single READ or WRITE operation for the DDR4 SDRAM consists of a single 8*n*-bit wide, four-clock data transfer at the internal DRAM core and two corresponding *n*-bit wide, one-half-clock-cycle data transfers at the I/O pins.

# **Industrial Temperature**

An industrial temperature (IT) device option requires that the case temperature not exceed below  $-40^{\circ}$ C or above 95°C. JEDEC specifications require the refresh rate to double when T<sub>C</sub> exceeds 85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance and the input/output impedance must be derated when operating outside of the commercial temperature range, when T<sub>C</sub> is between  $-40^{\circ}$ C and  $0^{\circ}$ C.

# **Automotive Temperature**

The automotive temperature (AT) device option requires that the case temperature not exceed below  $-40^{\circ}$ C or above  $105^{\circ}$ C. The specifications require the refresh rate to 2X when T<sub>C</sub> exceeds  $85^{\circ}$ C; 4X when T<sub>C</sub> exceeds  $95^{\circ}$ C. Additionally, ODT resistance and the input/output impedance must be derated when operating temperature Tc < $0^{\circ}$ C.

# **General Notes**

- The functionality and the timing specifications discussed in this data sheet are for the DLL enable mode of operation (normal operation), unless specifically stated otherwise.

- Throughout the data sheet, the various figures and text refer to DQs as "DQ." The DQ term is to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

- The terms "\_t" and "\_c" are used to represent the true and complement of a differential signal pair. These terms replace the previously used notation of "#" and/or overbar characters. For example, differential data strobe pair DQS, DQS# is now referred to as DQS\_t, DQS\_c.

- The term "\_n" is used to represent a signal that is active LOW and replaces the previously used "#" and/or overbar characters. For example: CS# is now referred to as CS\_n.

- The terms "DQS" and "CK" found throughout the data sheet are to be interpreted as DQS\_t, DQS\_c and CK\_t, CK\_c respectively, unless specifically stated otherwise.

- Complete functionality may be described throughout the entire document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- Any specific requirement takes precedence over a general statement.

- Any functionality not specifically stated here within is considered undefined, illegal, and not supported, and can result in unknown operation.

- Addressing is denoted as BG[n] for bank group, BA[n] for bank address, and A[n] for row/col address.

- The NOP command is not allowed, except when exiting maximum power savings mode or when entering gear-down mode, and only a DES command should be used.

- Not all features described within this document may be available on the Rev. A (first) version.

- Not all specifications listed are finalized industry standards; best conservative estimates have been provided when an industry standard has not been finalized.

- Although it is implied throughout the specification, the DRAM must be used after V<sub>DD</sub> has reached the stable power-on level, which is achieved by toggling CKE at least once every 8192 × <sup>t</sup>REFI. However, in the event CKE is fixed HIGH, toggling CS\_n at least once every 8192 × <sup>t</sup>REFI is an acceptable alternative. Placing the DRAM into self refresh mode also alleviates the need to toggle CKE.

- Not all features designated in the data sheet may be supported by earlier die revisions due to late definition by JEDEC.

- A x16 device's DQ bus is comprised of two bytes. If only one of the bytes needs to be used, use the lower byte for data transfers and terminate the upper byte as noted:

- Connect UDQS\_t to VDDQ or VSS/ VSSQ via a resistor in the 200 $\Omega$  range.

- Connect UDQS\_c to the opposite rail via a resistor in the same  $200\Omega$  range.

- Connect UDM to VDDQ via a large (10,000 $\Omega$ ) pull-up resistor.

- Connect UDBI to VDDQ via a large  $(10,000\Omega)$  pull-up resistor.

- Connect DQ [15:8] individually to VDDQ via a large  $(10,000\Omega)$  resistors, or float DQ [15:8].

# **Definitions of the Device-Pin Signal Level**

- HIGH: A device pin is driving the logic 1 state.

- LOW: A device pin is driving the logic 0 state.

- High-Z: A device pin is tri-state.

- ODT: A device pin terminates with the ODT setting, which could be terminating or tri-state depending on the mode register setting.

# **Definitions of the Bus Signal Level**

- HIGH: One device on the bus is HIGH, and all other devices on the bus are either ODT or High-Z. The voltage level on the bus is nominally  $V_{\rm DDO}$ .

- LOW: One device on the bus is LOW, and all other devices on the bus are either ODT or High-Z. The voltage level on the bus is nominally  $V_{OL(DC)}$  if ODT was enabled, or  $V_{SSQ}$  if High-Z.

- High-Z: All devices on the bus are High-Z. The voltage level on the bus is undefined as the bus is floating.

- ODT: At least one device on the bus is ODT, and all others are High-Z. The voltage level on the bus is nominally  $V_{DDQ}$ .

- The specification requires 8,192 refresh commands within 64ms between 0°C and 85°C. This allows for a <sup>t</sup>REFI of 7.8125µs (the use of "7.8µs" is truncated from 7.8125µs). The specification also requires 8,192 refresh commands within 32ms between 85°C and 95°C. This allows for a <sup>t</sup>REFI of 3.90625µs (the use of "3.9µs" is truncated from 3.90625µs).

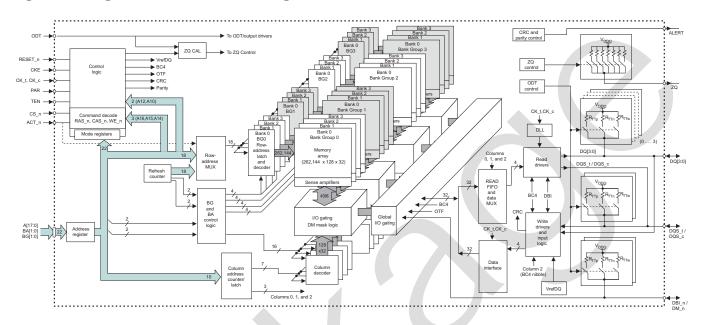

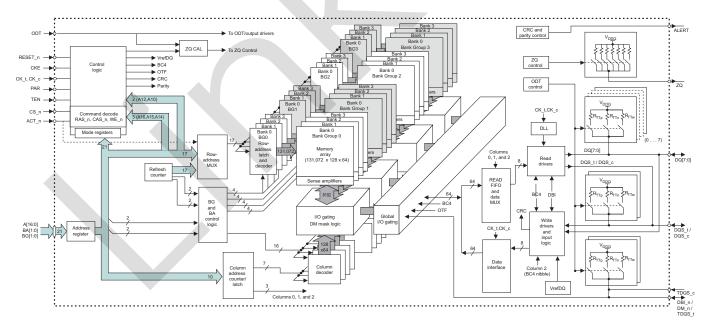

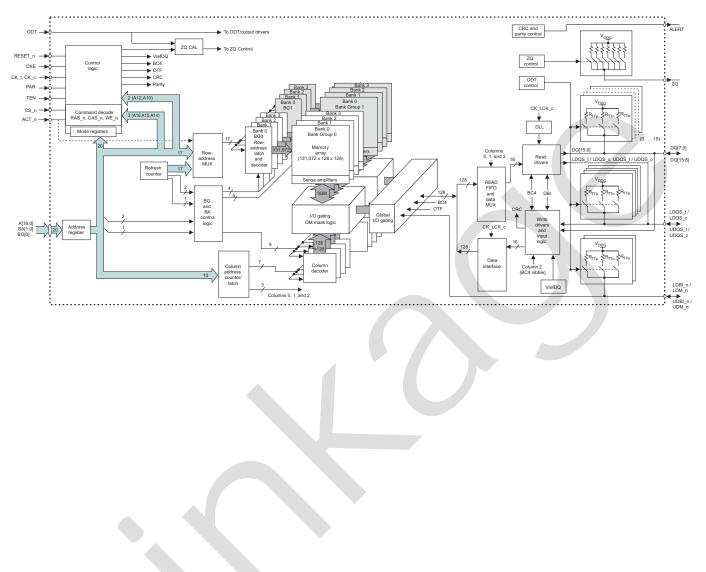

# **Functional Block Diagrams**

DDR4 SDRAM is a high-speed, CMOS dynamic random access memory. It is internally configured as an 16-bank (4-banks per Bank Group) DRAM.

Figure 2: 4 Gig x 4 Functional Block Diagram

Figure 3: 2 Gig x 8 Functional Block Diagram

# Figure 4: 1 Gig x 16 Functional Block Diagram

# 16Gb: x4, x8, x16 DDR4 SDRAM

# **Ball Assignments**

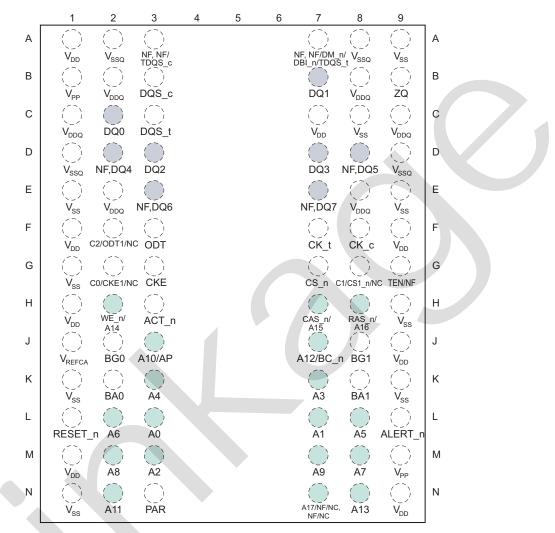

# Figure 5: 78-Ball x4, x8 Ball Assignments

Notes: 1. See Ball Descriptions.

- 2. A comma "," separates the configuration; a slash "/" defines a mode register selectable function, command/address function, density, or package dependence.

- 3. Address bits (including bank groups) are density- and configuration-dependent (see Addressing).

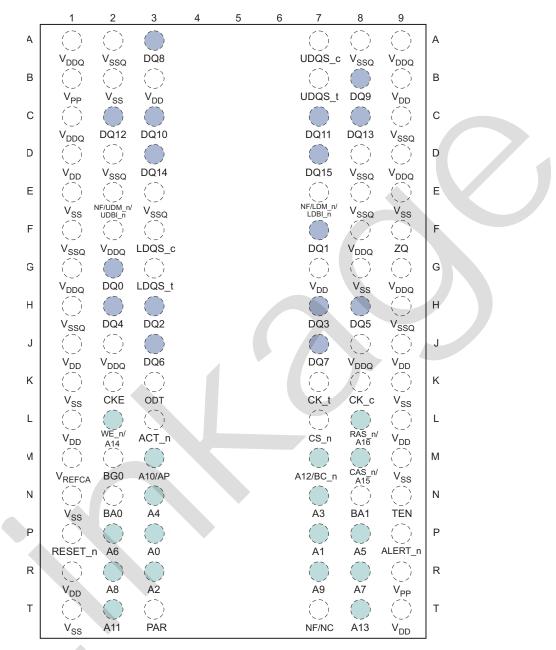

# Figure 6: 96-Ball x16 Ball Assignments

## Notes: 1. See Ball Descriptions.

- 2. A slash "/" defines a mode register selectable function, command/address function, density, or package dependence.

- 3. Address bits (including bank groups) are density- and configuration-dependent (see Addressing).

# **Ball Descriptions**

The pin description table below is a comprehensive list of all possible pins for DDR4 devices. All pins listed may not be supported on the device defined in this data sheet. See the Ball Assignments section to review all pins used on this device.

# **Ball Descriptions**

| Symbol                           | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[17:0]                          | Input | <b>Address inputs:</b> Provide the row address for ACTIVATE commands and the column address for READ/WRITE commands to select one location out of the memory array in the respective bank. (A10/AP, A12/BC_n, WE_n/A14, CAS_n/A15, RAS_n/A16 have additional functions, see individual entries in this table.) The address inputs also provide the op-code during the MODE REGISTER SET command. A16 is used on some 8Gb and 16Gb parts. A17 connection is part-number specific; Contact vendor for more information.                                                                                                                                                             |

| A10/AP                           | Input | <b>Auto precharge:</b> A10 is sampled during READ and WRITE commands to determine whether auto precharge should be performed to the accessed bank after a READ or WRITE operation. (HIGH = auto precharge; LOW = no auto precharge.) A10 is sampled during a PRECHARGE command to determine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by the bank group and bank addresses.                                                                                                                                                                                                         |

| A12/BC_n                         | Input | <b>Burst chop:</b> A12/BC_n is sampled during READ and WRITE commands to determine if burst chop (on-the-fly) will be performed. (HIGH = no burst chop; LOW = burst chopped). See the Command Truth Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACT_n                            | Input | <b>Command input:</b> ACT_n indicates an ACTIVATE command. When ACT_n (along with CS_n) is LOW, the input pins RAS_n/A16, CAS_n/A15, and WE_n/A14 are treated as row address inputs for the ACTIVATE command. When ACT_n is HIGH (along with CS_n LOW), the input pins RAS_n/ A16, CAS_n/A15, and WE_n/A14 are treated as normal commands that use the RAS_n, CAS_n, and WE_n signals. See the Command Truth Table.                                                                                                                                                                                                                                                               |

| BA[1:0]                          | Input | <b>Bank address inputs:</b> Define the bank (within a bank group) to which an ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. Also determines which mode register is to be accessed during a MODE REGISTER SET command.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BG[1:0]                          | Input | <b>Bank group address inputs:</b> Define the bank group to which an ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. Also determines which mode register is to be accessed during a MODE REGISTER SET command. BG[1:0] are used in the x4 and x8 configurations. BG1 is not used in the x16 configuration.                                                                                                                                                                                                                                                                                                                                                           |

| C0/CKE1,<br>C1/CS1_n,<br>C2/ODT1 | Input | <b>Stack address inputs:</b> These inputs are used only when devices are stacked; that is, they are used in 2H, 4H, and 8H stacks for x4 and x8 configurations (these pins are not used in the x16 configuration, and are NC on the x4/x8 SDP). DDR4 will support a traditional DDP package, which uses these three signals for control of the second die (CS1_n, CKE1, ODT1). DDR4 is not expected to support a traditional QDP package. For all other stack configurations, such as a 4H or 8H, it is assumed to be a single-load (master/slave) type of configuration where C0, C1, and C2 are used as chip ID selects in conjunction with a single CS_n, CKE, and ODT signal. |

| CK_t,<br>CK_c                    | Input | <b>Clock:</b> Differential clock inputs. All address, command, and control input signals are sampled on the crossing of the positive edge of CK_t and the negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **Ball Descriptions (Continued)**

| Symbol                               | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СКЕ                                  | Input | <b>Clock enable:</b> CKE HIGH activates and CKE LOW deactivates the internal clock signals, device input buffers, and output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or active power-down (row active in any bank). CKE is asynchronous for self refresh exit, however, timing parameters such as <sup>t</sup> XS are still calculated from the first rising clock edge where CKE HIGH satisfies <sup>t</sup> IS. After V <sub>REFCA</sub> has become stable during the power-on and initializa-                                                                                                        |

|                                      |       | tion sequence, it must be maintained during all operations (including SELF REFRESH).<br>CKE must be maintained HIGH throughout read and write accesses. Input buffers<br>(excluding CK_t, CK_c, ODT, RESET_n, and CKE) are disabled during power-down.<br>Input buffers (excluding CKE and RESET_n) are disabled during self refresh.                                                                                                                                                                                                                                                                                                                               |

| CS_n                                 | Input | <b>Chip select:</b> All commands are masked when CS_n is registered HIGH. CS_n provides for external rank selection on systems with multiple ranks. CS_n is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DM_n,<br>UDM_n<br>LDM_n              | Input | <b>Input data mask:</b> DM_n is an input mask signal for write data. Input data is masked when DM is sampled LOW coincident with that input data during a write access. DM is sampled on both edges of DQS. DM is not supported on x4 configurations. The UDM_n and LDM_n pins are used in the x16 configuration: UDM_n is associated with DQ[15:8]; LDM_n is associated with DQ[7:0]. The DM, DBI, and TDQS functions are enabled by mode register settings. See the Data Mask section.                                                                                                                                                                            |

| ODT                                  | Input | <b>On-die termination:</b> ODT (registered HIGH) enables termination resistance internal to the DDR4 SDRAM. When enabled, ODT ( $R_{TT}$ ) is applied only to each DQ, DQS_t, DQS_c, DM_n/DBI_n/TDQS_t, and TDQS_c signal for the x4 and x8 configurations (when the TDQS function is enabled via mode register). For the x16 configuration, $R_{TT}$ is applied to each DQ, UDQS_t, UDQS_c, LDQS_t, LDQS_c, UDM_n, and LDM_n signal. The ODT pin will be ignored if the mode registers are programmed to disable $R_{TT}$ .                                                                                                                                        |

| PAR                                  | Input | <b>Parity for command and address:</b> This function can be enabled or disabled via the mode register. When enabled, the parity signal covers all command and address inputs, including ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, A[17:0], A10/AP, A12/BC_n, BA[1:0], and BG[1:0] with C0, C1, and C2 on 3DS only devices. Control pins NOT covered by the parity signal are CS_n, CKE, and ODT. Unused address pins that are density- and configuration-specific should be treated internally as 0s by the DRAM parity logic. Command and address inputs will have parity check performed when commands are latched via the rising edge of CK_t and when CS_n is LOW. |

| RAS_n/A16,<br>CAS_n/A15,<br>WE_n/A14 | Input | <b>Command inputs:</b> RAS_n/A16, CAS_n/A15, and WE_n/A14 (along with CS_n and ACT_n) define the command and/or address being entered. See the ACT_n description in this table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RESET_n                              | Input | Active LOW asynchronous reset: Reset is active when RESET_n is LOW, and inac-<br>tive when RESET_n is HIGH. RESET_n must be HIGH during normal operation. RESET_n<br>is a CMOS rail-to-rail signal with DC HIGH and LOW at 80% and 20% of V <sub>DD</sub> (960 mV<br>for DC HIGH and 240 mV for DC LOW).                                                                                                                                                                                                                                                                                                                                                            |

| TEN                                  | Input | <b>Connectivity test mode:</b> TEN is active when HIGH and inactive when LOW. TEN must be LOW during normal operation. TEN is a CMOS rail-to-rail signal with DC HIGH and LOW at 80% and 20% of V <sub>DD</sub> (960mV for DC HIGH and 240mV for DC LOW). On Linkage 3DS devices, connectivity test mode is not supported and the TEN pin should be considered NF maintained LOW at all times.                                                                                                                                                                                                                                                                      |

# **Ball Descriptions (Continued)**

| Symbol                                                      | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ                                                          | I/O       | <b>Data input/output:</b> Bidirectional data bus. DQ represents DQ[3:0], DQ[7:0], and DQ[15:0] for the x4, x8, and x16 configurations, respectively. If write CRC is enabled via mode register, the write CRC code is added at the end of data burst. Any one or all of DQ0, DQ1, DQ2, and DQ3 may be used to monitor the internal V <sub>REF</sub> level during test via mode register setting MR[4] A[4] = HIGH, training times change when enabled. During this mode, the R <sub>TT</sub> value should be set to High-Z. This measurement is for verification purposes and is NOT an external voltage supply pin.          |

| DBI_n,<br>UDBI_n,<br>LDBI_n                                 | I/O       | <b>DBI input/output:</b> Data bus inversion. DBI_n is an input/output signal used for data bus inversion in the x8 configuration. UDBI_n and LDBI_n are used in the x16 configuration; UDBI_n is associated with DQ[15:8], and LDBI_n is associated with DQ[7:0]. The DBI feature is not supported on the x4 configuration. DBI is not supported for 3DS devices and should be disabled in MR5. DBI can be configured for both READ (output) and WRITE (input) operations depending on the mode register settings. The DM, DBI, and TDQS functions are enabled by mode register settings. See the Data Bus Inversion section. |

| DQS_t,<br>DQS_c,<br>UDQS_t,<br>UDQS_c,<br>LDQS_t,<br>LDQS_c | I/O       | <b>Data strobe:</b> Output with READ data, input with WRITE data. Edge-aligned with READ data, centered-aligned with WRITE data. For the x16, LDQS corresponds to the data on DQ[7:0]; UDQS corresponds to the data on DQ[15:8]. For the x4 and x8 configurations, DQS corresponds to the data on DQ[3:0] and DQ[7:0], respectively. DDR4 SDRAM supports a differential data strobe only and does not support a single-ended data strobe.                                                                                                                                                                                     |

| ALERT_n                                                     | Output    | <b>Alert output:</b> This signal allows the DRAM to indicate to the system's memory controller that a specific alert or event has occurred. Alerts will include the command/address parity error and the CRC data error when either of these functions is enabled in the mode register.                                                                                                                                                                                                                                                                                                                                       |

| TDQS_t,<br>TDQS_c                                           | Output    | <b>Termination data strobe:</b> TDQS_t and TDQS_c are used by x8 DRAMs only. When enabled via the mode register, the DRAM will enable the same R <sub>TT</sub> termination resistance on TDQS_t and TDQS_c that is applied to DQS_t and DQS_c. When the TDQS function is disabled via the mode register, the DM/TDQS_t pin will provide the DATA MASK (DM) function, and the TDQS_c pin is not used. The TDQS function must be disabled in the mode register for both the x4 and x16 configurations. The DM function is supported only in x8 and x16 configurations.                                                          |

| V <sub>DD</sub>                                             | Supply    | <b>Power supply:</b> 1.2V ±0.060V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DDQ</sub>                                            | Supply    | DQ power supply: 1.2V ±0.060V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>PP</sub>                                             | Supply    | DRAM activating power supply: 2.5V -0.125V/+0.250V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>REFCA</sub>                                          | Supply    | Reference voltage for control, command, and address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub>                                             | Supply    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SSQ</sub>                                            | Supply    | DQ ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ZQ                                                          | Reference | Reference ball for ZQ calibration: This ball is tied to an external 240 $\Omega$ resistor (RZQ), which is tied to $V_{SSQ}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RFU                                                         | -         | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC                                                          | -         | No connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NF                                                          | -         | <b>No function:</b> Internal connection is present but has no function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

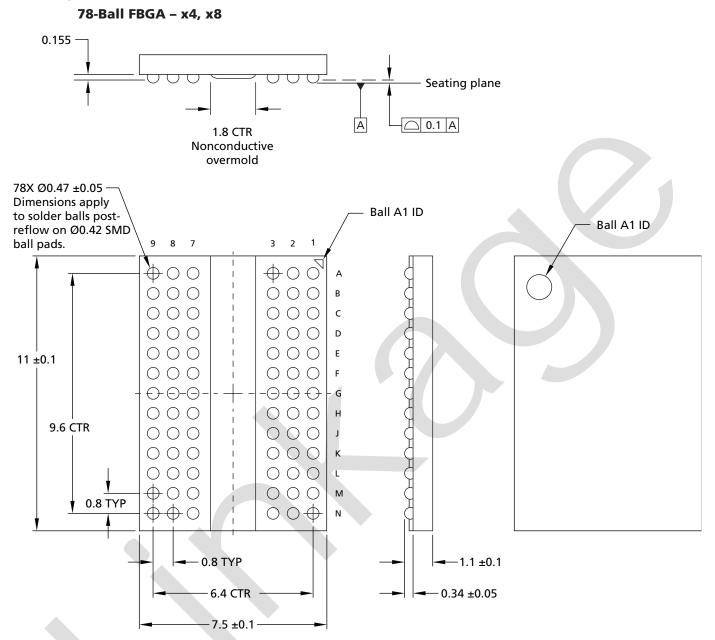

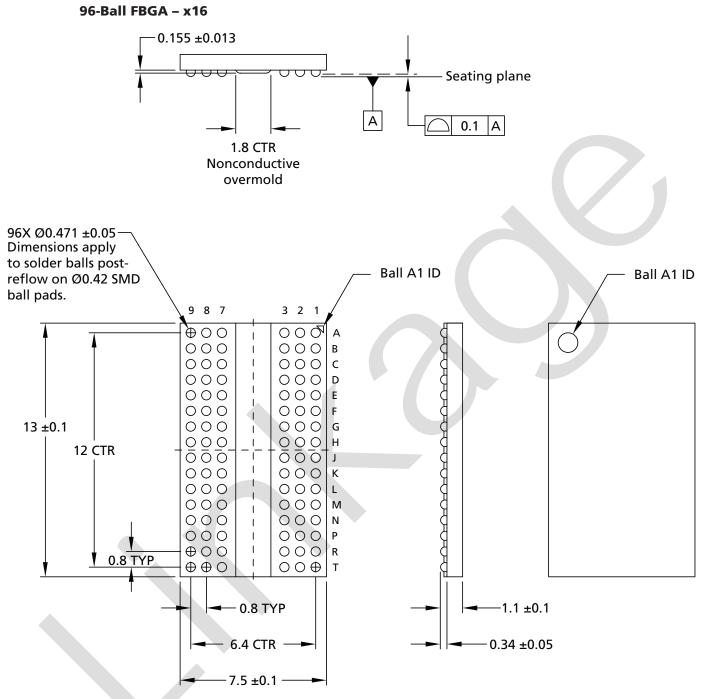

# **Package Dimensions**

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC305 (96.5% Sn, 3% Ag, 0.5% Cu).

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC305 (96.5% Sn, 3% Ag, 0.5% Cu).

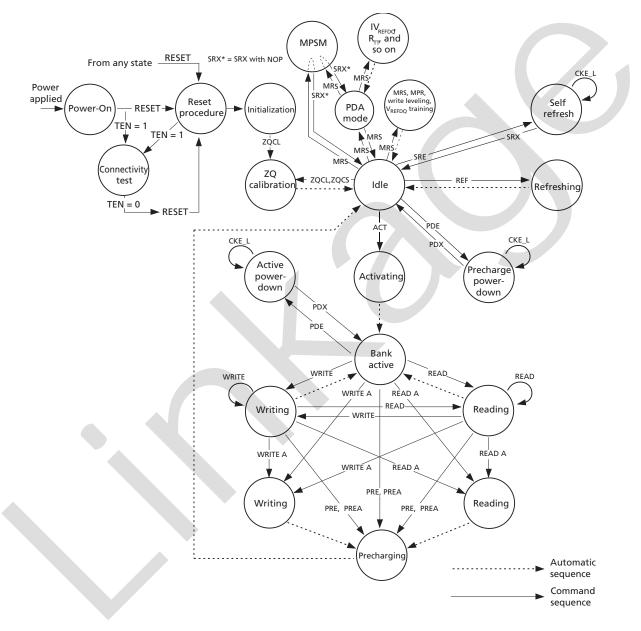

# **State Diagram**

This simplified state diagram provides an overview of the possible state transitions and the commands to control them. Situations involving more than one bank, the enabling or disabling of on-die termination, and some other events are not captured in full detail.

# **Simplified State Diagram**

# **State Diagram Command Definitions**

| Command | Description                        |

|---------|------------------------------------|

| ACT     | Active                             |

| MPR     | Multipurpose register              |

| MRS     | Mode register set                  |

| PDE     | Enter power-down                   |

| PDX     | Exit power-down                    |

| PRE     | Precharge                          |

| PREA    | Precharge all                      |

| READ    | RD, RDS4, RDS8                     |

| READ A  | RDA, RDAS4, RDAS8                  |

| REF     | Refresh, fine granularity refresh  |

| RESET   | Start reset procedure              |

| SRE     | Self refresh entry                 |

| SRX     | Self refresh exit                  |

| TEN     | Boundary scan mode enable          |

| WRITE   | WR, WRS4, WRS8 with/without CRC    |

| WRITE A | WRA, WRAS4, WRAS8 with/without CRC |

| ZQCL    | ZQ calibration long                |

| ZQCS    | ZQ calibration short               |

Notes: 1. See the Command Truth Table for more details.

# **Functional Description**

The DDR4 SDRAM is a high-speed dynamic random-access memory internally configured as sixteen banks (4 bank groups with 4 banks for each bank group) for x4/x8 devices, and as eight banks for each bank group (2 bank groups with 4 banks each) for x16 devices. The device uses double data rate (DDR) architecture to achieve high-speed operation. DDR4 architecture is essentially an 8*n*-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for a device module effectively consists of a single 8*n*-bit-wide, four-clock-cycle-data transfer at the internal DRAM core and eight corresponding *n*-bit-wide, one-half-clock-cycle data transfers at the I/O pins.

Read and write accesses to the device are burst-oriented. Accesses start at a selected location and continue for a burst length of eight or a chopped burst of four in a programmed sequence. Operation begins with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BG[1:0] select the bank group for x4/x8, and BG0 selects the bank group for x16; BA[1:0] select the bank, and A[17:0] select the row. See the Addressing section for more details). The address bits registered coincident with the READ or WRITE command are used to select the starting column location for the burst operation, determine if the auto PRECHARGE command is to be issued (via A10), and select BC4 or BL8 mode on-the-fly (OTF) (via A12) if enabled in the mode register.

Prior to normal operation, the device must be powered up and initialized in a predefined manner. The following sections provide detailed information covering device reset and initialization, register definition, command descriptions, and device operation.

NOTE: The use of the NOP command is allowed only when exiting maximum power saving mode or when entering gear-down mode.

# **RESET and Initialization Procedure**

To ensure proper device function, the power-up and reset initialization default values for the following mode register (MR) settings are defined as:

- Gear-down mode (MR3 A[3]): 0 = 1/2 rate

- Per-DRAM addressability (MR3 A[4]): 0 = disable

- Maximum power-saving mode (MR4 A[1]): 0 = disable

- CS to command/address latency (MR4 A[8:6]): 000 = disable

- CA parity latency mode (MR5 A[2:0]): 000 = disable

- Hard post package repair mode (MR4 A[13]): 0 = disable

- Soft post package repair mode (MR4 A[5]): 0 = disable

# **Power-Up and Initialization Sequence**

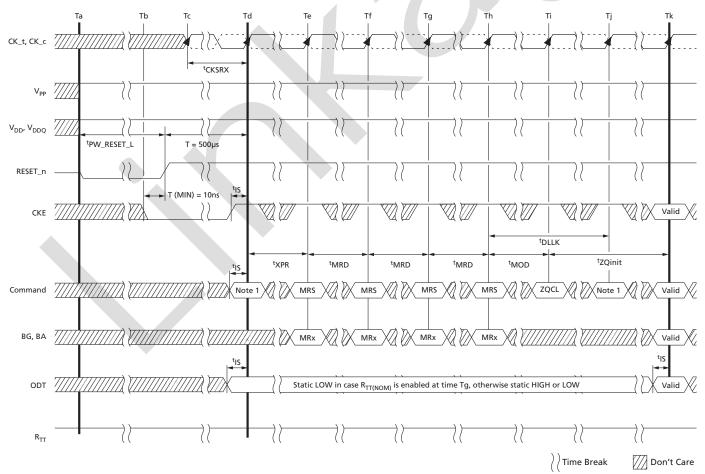

The following sequence is required for power-up and initialization:

1. Apply power (RESET\_n and TEN should be maintained below  $0.2 \times V_{DD}$  while supplies ramp up; all other inputs may be undefined). When supplies have ramped to a valid stable level, RESET\_n must be maintained below  $0.2 \times V_{DD}$  for a minimum of <sup>t</sup>PW\_RESET\_L and TEN must be maintained below  $0.2 \times V_{DD}$  for a minimum of 700µs. CKE is pulled LOW anytime before RESET\_n is de-asserted (minimum time of 10ns). The power voltage ramp time between 300mV to  $V_{DD,min}$  must be no greater than 200ms, and during the ramp,  $V_{DD}$  must be greater than or equal to  $V_{DDQ}$  and  $(V_{DD} - V_{DDQ}) < 0.3V$ .  $V_{PP}$  must ramp at the same time or up to 10 minutes prior to  $V_{DD}$ , and  $V_{PP}$  must be equal to or higher than  $V_{DD}$  at all times. The total time for which  $V_{PP}$  is powered and  $V_{DD}$  is unpowered should not exceed 360 cumulative hours. After  $V_{DD}$  has ramped and reached a stable level, RESET\_n must go high within 10 minutes. After RESET\_n goes high, the initialization sequence must be started within 3 seconds. For debug purposes, the 10 minute and 3 second delay limits may be extended to 60 minutes each provided the DRAM is operated in this debug mode for no more than 360 cumulative hours.

During power-up, the supply slew rate is governed by the limits stated in the table below and either condition A or condition B listed below must be met.

| Symbol                                                         | Min   | Мах | Unit | Comment                                                                   |

|----------------------------------------------------------------|-------|-----|------|---------------------------------------------------------------------------|

| V <sub>DD</sub> _SL, V <sub>DDQ</sub> _SL, V <sub>PP</sub> _SL | 0.004 | 600 | V/ms | Measured between 300mV and 80% of supply minimum                          |

| V <sub>DD</sub> ona                                            | N/A   | 200 | ms   | $\rm V_{\rm DD}$ maximum ramp time from 300mV to $\rm V_{\rm DD}$ minimum |

| V <sub>DDQ</sub> ona                                           | N/A   | 200 | ms   | $V_{\rm DDQ}$ maximum ramp time from 300mV to $V_{\rm DDQ}$ minimum       |

# **Supply Power-up Slew Rate**

Notes: 1. 20 MHz band-limited measurement.

– Condition A:

- Apply  $V_{PP}$  without any slope reversal before or at the same time as  $V_{DD}$  and  $V_{DDQ}$ .

- $V_{DD}$  and  $V_{DDQ}$  are driven from a single-power converter output and apply  $V_{DD}/V_{DDQ}$  without any slope reversal before or at the same time as  $V_{TT}$  and  $V_{REFCA}$ .

- The voltage levels on all balls other than  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ , and  $V_{SSQ}$  must be less than or equal to  $V_{DDQ}$  and  $V_{DD}$  on one side and must be greater than or equal to  $V_{SSQ}$  and  $V_{SS}$  on the other side.

- +  $V_{TT}$  is limited to 0.76V MAX when the power ramp is complete.

- V<sub>REFCA</sub> tracks V<sub>DD</sub>/2.

- Condition B:

- Apply  $V_{\text{PP}}$  without any slope reversal before or at the same time as  $V_{\text{DD}}.$

- Apply  $V_{DD}$  without any slope reversal before or at the same time as  $V_{DDQ}$ .

- Apply  $V_{DDQ}$  without any slope reversal before or at the same time as  $V_{TT}$  and  $V_{REFCA}$ .

- The voltage levels on all pins other than  $V_{PP}$ ,  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ , and  $V_{SSQ}$  must be less than or equal to  $V_{DDQ}$  and  $V_{DD}$  on one side and must be larger than or equal to  $V_{SSQ}$  and  $V_{SS}$  on the other side.

- 2. After RESET\_n is de-asserted, wait for a minimum of 500µs, but no longer than 3 seconds, before allowing CKE to be registered HIGH at clock edge Td. During this time, the device will start internal state initialization; this will be done independently of external clocks. A reasonable attempt was made in the design to power up with the following default MR settings: gear-down mode (MR3 A[3]): 0 = 1/2 rate; per-DRAM addressability (MR3 A[4]): 0 = disable; maximum power-down (MR4 A[1]): 0 = disable; CS to command/address latency (MR4 A[8:6]): 000 = disable; CA parity latency mode (MR5 A[2:0]): 000 = disable. However, it should be assumed that at power up the MR settings are undefined and should be programmed as shown below.

- 3. Clocks (CK\_t, CK\_c) need to be started and stabilized for at least 10ns or 5 <sup>t</sup>CK (whichever is larger) before CKE is registered HIGH at clock edge Td. Because CKE is a synchronous signal, the corresponding setup time to clock (<sup>t</sup>IS) must be met. Also, a DESELECT command must be registered (with <sup>t</sup>IS setup time to clock) at clock edge Td. After the CKE is registered HIGH after RESET, CKE needs to be continuously registered HIGH until the initialization sequence is finished, including expiration of <sup>t</sup>DLLK and <sup>t</sup>ZQinit.

- 4. The device keeps its ODT in High-Z state as long as RESET\_n is asserted. Further, the SDRAM keeps its ODT in High-Z state after RESET\_n de-assertion until CKE is registered HIGH. The ODT input signal may be in an undefined state until <sup>t</sup>IS before CKE is registered HIGH. When CKE is registered HIGH, the ODT input signal may be statically held either LOW or HIGH. If R<sub>TT(NOM)</sub> is to be enabled in MR1, the ODT input signal must be statically held LOW. In all cases, the ODT input signal remains static until the power-up initialization sequence is finished, including the expiration of <sup>t</sup>DLLK and <sup>t</sup>ZQinit.

- 5. After CKE is registered HIGH, wait a minimum of RESET CKE EXIT time, <sup>t</sup>XPR, before issuing the first MRS command to load mode register (<sup>t</sup>XPR = MAX (<sup>t</sup>XS, 5 × <sup>t</sup>CK).

- 6. Issue MRS command to load MR3 with all application settings, wait <sup>t</sup>MRD.

- 7. Issue MRS command to load MR6 with all application settings, wait <sup>t</sup>MRD.

- 8. Issue MRS command to load MR5 with all application settings, wait <sup>t</sup>MRD.

- 9. Issue MRS command to load MR4 with all application settings, wait <sup>t</sup>MRD.

- 10.Issue MRS command to load MR2 with all application settings, wait <sup>t</sup>MRD.

- 11.Issue MRS command to load MR1 with all application settings, wait <sup>t</sup>MRD.

12.Issue MRS command to load MR0 with all application settings, wait <sup>t</sup>MOD.

13.Issue a ZQCL command to start ZQ calibration.

14.Wait for <sup>t</sup>DLLK and <sup>t</sup>ZQinit to complete.

- 15.The device will be ready for normal operation. Once the DRAM has been initialized, if the DRAM is in an idle state longer than 960ms, then either (a) REF commands must be issued within <sup>t</sup>REFI constraints (specification for posting allowed) or (b) CKE or CS\_n must toggle once within every 960ms interval of idle time. For debug purposes, the 960ms delay limit maybe extended to 60 minutes provided the DRAM is operated in this debug mode for no more than 360 cumulative hours.

- 16.Optional MBIST-PPR mode can be entered by setting MR4:A0 to 1, followed by subsequent MR0 guard key sequences, then DRAM will drive ALERT\_n to LOW. DRAM will drive ALERT\_n to HIGH

to indicate that this operation is completed. MBIST-PPR mode can take place anytime after Tk. Note that no exit sequence or re-initialization is needed after MBIST completes; As soon as ALERT\_N goes HIGH and <sup>t</sup>IS is satisfied, MR0 must be re-written to the pre guard key state, then and the DRAM is immediately ready to receive valid commands.

A stable valid  $V_{DD}$  level is a set DC level (0Hz to 250 KHz) and must be no less than  $V_{DD,min}$  and no greater than V<sub>DD.max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is stable. AC noise of ±60mV (greater than 250 KHz) is allowed on V<sub>DD</sub> provided the noise doesn't alter V<sub>DD</sub> to less than V<sub>DD,min</sub> or greater than V<sub>DD.max</sub>.

Linkage

A stable valid V<sub>DDO</sub> level is a set DC level (0Hz to 250 KHz) and must be no less than V<sub>DDO,min</sub> and no greater than V<sub>DDO,max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is stable. AC noise of ±60mV (greater than 250 KHz) is allowed on  $V_{DDO}$  provided the noise doesn't alter  $V_{DDO}$  to less than  $V_{DDO,min}$  or greater than V<sub>DDO.max</sub>.

A stable valid V<sub>PP</sub> level is a set DC level (0Hz to 250 KHz) and must be no less than V<sub>PP,min</sub> and no greater than V<sub>PP,max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is stable. AC noise of ±120mV (greater than 250 KHz) is allowed on V<sub>PP</sub> provided the noise doesn't alter V<sub>PP</sub> to less than V<sub>PP,min</sub> or greater than V<sub>PP,max</sub>.

# Figure 14: RESET and Initialization Sequence at Power-On Ramping

- Notes: 1. From time point Td until Tk, a DES command must be applied between MRS and ZQCL commands.

- 2. MRS commands must be issued to all mode registers that have defined settings.

- 3. In general, there is no specific sequence for setting the MRS locations (except for dependent or co-related features, such as ENABLE DLL in MR1 prior to RESET DLL in MR0, for example).

- 4. TEN is not shown; however, it is assumed to be held LOW.

- 5. Optional MBIST-PPR may be entered any time after Tk.

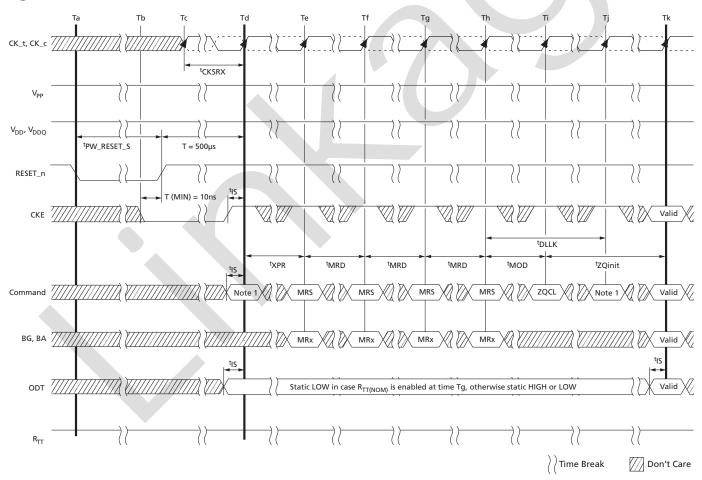

# **RESET Initialization with Stable Power Sequence**

The following sequence is required for RESET at no power interruption initialization:

- 1. Assert RESET\_n below  $0.2 \times V_{DD}$  any time when reset is needed (all other inputs may be undefined).

- RESET\_n needs to be maintained for minimum <sup>t</sup>PW\_RESET. CKE is pulled LOW before RESET\_n being de-asserted (minimum time 10ns).

- 2. Follow Steps 2 through 10 in the Reset and Initialization Sequence at Power-On Ramping procedure.

When the reset sequence is complete, all counters except the refresh counters have been reset and the device is ready for normal operation.

# Figure 7: RESET Procedure at Power Stable Condition

Notes: 1. From time point Td until Tk, a DES command must be applied between MRS and ZQCL commands. 2. MRS commands must be issued to all mode registers that have defined settings.

- 3. In general, there is no specific sequence for setting the MRS locations (except for dependent or co-related features, such as ENABLE DLL in MR1 prior to RESET DLL in MR0, for example).

- 4. TEN is not shown; however, it is assumed to be held LOW.

# **Uncontrolled Power-Down Sequence**

In the event of an uncontrolled ramping down of  $V_{PP}$  supply,  $V_{PP}$  is allowed to be less than  $V_{DD}$  provided the following conditions are met:

- Condition A:  $V_{PP}$  and  $V_{DD}/V_{DDQ}$  are ramping down (as part of turning off) from normal operating levels.

- Condition B: The amount that  $V_{\rm PP}$  may be less than  $V_{\rm DD}/V_{\rm DDQ}$  is less than or equal to 500mV.

- Condition C: The time  $V_{PP}$  may be less than  $V_{DD}$  is  $\leq 10$ ms per occurrence with a total accumulated time in this state  $\leq 100$ ms.

- Condition D: The time  $V_{PP}$  may be less than 2.0V and above  $V_{SS}$  while turning off is  $\leq 15$ ms per occurrence with a total accumulated time in this state  $\leq 150$ ms.

# **Electrical Specifications**

# **Absolute Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability. Although "unlimited" row accesses to the same row is allowed within the refresh period; excessive row accesses to the same row over a long term can result in degraded operation.

# **Absolute Maximum Ratings**

| Symbol                             | Parameter                                                  | Min  | Мах | Unit | Notes |

|------------------------------------|------------------------------------------------------------|------|-----|------|-------|

| V <sub>DD</sub>                    | Voltage on $V_{DD}$ pin relative to $V_{SS}$               | -0.4 | 1.5 | V    | 1     |

| V <sub>DDQ</sub>                   | Voltage on $V_{DDQ}$ pin relative to $V_{SS}$              | -0.4 | 1.5 | V    | 1     |

| V <sub>PP</sub>                    | Voltage on V <sub>PP</sub> pin relative to V <sub>SS</sub> | -0.4 | 3.0 | V    | 3     |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub>             | -0.4 | 1.5 | V    |       |

| T <sub>STG</sub>                   | Storage temperature                                        | -55  | 150 | °C   | 2     |

Notes: 1.  $V_{DD}$  and  $V_{DDQ}$  must be within 300mV of each other at all times, and  $V_{REF}$  must not be greater than 0.6 ×  $V_{DDQ}$ . When  $V_{DD}$  and  $V_{DDO}$  are <500mV,  $V_{REF}$  can be ≤300mV.

- 2. Storage temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to the JESD51-2 standard.

- 3.  $V_{PP}$  must be equal to or greater than  $V_{DD}/V_{DDQ}$  at all times when powered.

# **DRAM Component Operating Temperature Range**

Operating temperature, T<sub>OPER</sub>, is the case surface temperature on the center/top side of the DRAM. For measurement conditions, refer to the JEDEC document JESD51-2.

# **Temperature Range**

| Symbol            | Parameter                             | Min | Мах | Unit | Notes |

|-------------------|---------------------------------------|-----|-----|------|-------|

| T <sub>OPER</sub> | Normal operating temperature range    | -40 | 85  | °C   | 1     |

|                   | Extended temperature range (optional) | >85 | 105 | °C   | 2     |

Notes: 1. The normal temperature range specifies the temperatures at which all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0°C to 85°C under all operating conditions for the commercial offering; The industrial and automotive temperature offerings allow the case temperature to go below 0°C to -40°C.

- 2. Some applications require operation of the commercial, industrial, and automotive temperature DRAMs in the extended temperature range (between 85°C and 105°C case temperature). Full specifications are supported in this range, but the following additional conditions apply:

- Refer to tREFI and tRFC parameters table for tREFI requirements when operating above 85°C

- If SELF REFRESH operation is required in the extended temperature range, it is mandatory to use either the manual self refresh mode with extended temperature range capability (MR2[6] = 0 and MR2[7] = 1) or enable the optional auto self refresh mode (MR2[6] = 1 and MR2[7] = 1).

# **Electrical Characteristics – AC and DC Operating Conditions**

# **Supply Operating Conditions**

| Symbol           | Parameter                    | Rating |     |     | Unit   | Notes         |  |

|------------------|------------------------------|--------|-----|-----|--------|---------------|--|

|                  |                              | Min    | Тур | Мах |        |               |  |

| V <sub>DD</sub>  | Supply voltage               | 1.14   | 1.2 |     | 1.26V  | 1, 2, 3, 4, 5 |  |

| V <sub>DDQ</sub> | Supply voltage<br>for output | 1.14   | 1.2 |     | 1.26V  | 1, 2, 6       |  |

| V <sub>PP</sub>  | Wordline sup-<br>ply voltage | 2.375  | 2.5 |     | 2.750V | 7             |  |

# **Recommended Supply Operating Conditions**

Notes: 1. Under all conditions  $V_{DDQ}$  must be less than or equal to  $V_{DD}$ .

- 2.  $V_{DDQ}$  tracks with  $V_{DD}$ . AC parameters are measured with  $V_{DD}$  and  $V_{DDQ}$  tied together.

- 3. V<sub>DD</sub> slew rate between 300mV and 80% of V<sub>DD,min</sub> shall be between 0.004 V/ms and 600 V/ms, 20 MHz band-limited measurement.

- 4.  $V_{\text{DD}}$  ramp time from 300mV to  $V_{\text{DD},\text{min}}$  shall be no longer than 200ms.

- 5. A stable valid V<sub>DD</sub> level is a set DC level (0 Hz to 250 KHz) and must be no less than V<sub>DD,min</sub> and no greater than V<sub>DD,max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is final. AC noise of ±60mV (greater than 250 KHz) is allowed on V<sub>DD</sub> provided the noise doesn't alter V<sub>DD</sub> to less than V<sub>DD,min</sub> or greater than V<sub>DD,max</sub>.

- 6. A stable valid V<sub>DDQ</sub> level is a set DC level (0 Hz to 250 KHz) and must be no less than V<sub>DDQ,min</sub> and no greater than V<sub>DDQ,max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is final. AC noise of ±60mV (greater than 250 KHz) is allowed on V<sub>DDQ</sub> provided the noise doesn't alter V<sub>DDQ</sub> to less than V<sub>DDQ,min</sub> or greater than V<sub>DDQ,max</sub>.

- 7. A stable valid V<sub>PP</sub> level is a set DC level (0 Hz to 250 KHz) and must be no less than V<sub>PP,min</sub> and no greater than V<sub>PP,max</sub>. If the set DC level is altered anytime after initialization, the DLL reset and calibrations must be performed again after the new set DC level is final. AC noise of ±120mV (greater than 250 KHz) is allowed on V<sub>PP</sub> provided the noise doesn't alter V<sub>PP</sub> to less than V<sub>PP,min</sub> or greater than V<sub>PP,max</sub>.

# V<sub>DD</sub> Slew Rate

| Symbol             | Min Max |     | Unit | Notes |

|--------------------|---------|-----|------|-------|

| V <sub>DD_sl</sub> | 0.004   | 600 | V/ms | 1, 2  |

| V <sub>DD_on</sub> | -       | 200 | ms   | 3     |

Notes: 1. Measurement made between 300mV and 80% V<sub>DD</sub> (minimum level).

- 2. The DC bandwidth is limited to 20 MHz.

- 3. Maximum time to ramp  $V_{\text{DD}}$  from 300 mV to  $V_{\text{DD}}$  minimum.

# Leakages

# Leakages

| Condition                                           | Symbol              | Min | Мах | Unit | Notes |

|-----------------------------------------------------|---------------------|-----|-----|------|-------|

| Input leakage (excluding ZQ and TEN)                | I <sub>IN</sub>     | -2  | 2   | μΑ   | 1     |

| ZQ leakage                                          | I <sub>ZQ</sub>     | -50 | 10  | μΑ   | 1     |

| TEN leakage                                         | I <sub>TEN</sub>    | -6  | 10  | μΑ   | 1, 2  |

| V <sub>REFCA</sub> leakage                          | I <sub>VREFCA</sub> | -2  | 2   | μΑ   | 3     |

| Output leakage: V <sub>OUT</sub> = V <sub>DDQ</sub> | I <sub>OZpd</sub>   | -   | 10  | μΑ   | 4     |

| Output leakage: V <sub>OUT</sub> = V <sub>SSQ</sub> | I <sub>OZpu</sub>   | -50 | -   | μΑ   | 4, 5  |

Notes: 1. Input under test  $0V < V_{IN} < 1.1V$ .

- 2. Additional leakage due to weak pull-down.

- 3.  $V_{REFCA} = V_{DD}/2$ ,  $V_{DD}$  at valid level after initialization.

- 4. DQs are disabled.

- 5. ODT is disabled with the ODT input HIGH.

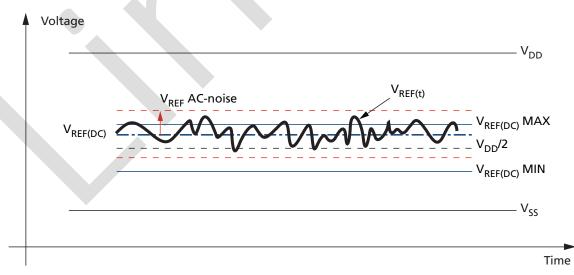

# **V<sub>REFCA</sub> Supply**

$V_{REFCA}$  is to be supplied to the DRAM and equal to  $V_{DD}/2$ . The  $V_{REFCA}$  is a reference supply input and therefore does not draw biasing current.

The DC-tolerance limits and AC-noise limits for the reference voltages  $V_{REFCA}$  are illustrated in the figure below. The figure shows a valid reference voltage  $V_{REF(t)}$  as a function of time ( $V_{REF}$  stands for  $V_{REFCA}$ ).  $V_{REF(DC)}$  is the linear average of  $V_{REF(t)}$  over a very long period of time (1 second). This average has to meet the MIN/MAX requirements. Furthermore,  $V_{REF(t)}$  may temporarily deviate from  $V_{REF(DC)}$  by no more than ±1%  $V_{DD}$  for the AC-noise limit.

# V<sub>REFDQ</sub> Voltage Range

The voltage levels for setup and hold time measurements are dependent on  $V_{REF}$ .  $V_{REF}$  is understood as  $V_{REF(DC)}$ , as defined in the above figure. This clarifies that DC-variations of  $V_{REF}$  affect the absolute

voltage a signal has to reach to achieve a valid HIGH or LOW level, and therefore, the time to which setup and hold is measured. System timing and voltage budgets need to account for  $V_{REF(DC)}$  deviations from the optimum position within the data-eye of the input signals. This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with  $V_{REF}$  AC-noise. Timing and voltage effects due to AC-noise on  $V_{REF}$  up to the specified limit (±1% of  $V_{DD}$ ) are included in DRAM timings and their associated deratings.

# **V<sub>REFDO</sub> Supply and Calibration Ranges**

The device internally generates its own  $V_{REFDQ}$ . DRAM internal  $V_{REFDQ}$  specification parameters: voltage range, step size,  $V_{REF}$  step time,  $V_{REF}$  full step time, and  $V_{REF}$  valid level are used to help provide estimated values for the internal  $V_{REFDQ}$  and are not pass/fail limits. The voltage operating range specifies the minimum required range for DDR4 SDRAM devices. The minimum range is defined by  $V_{REFDQ,min}$  and  $V_{REFDQ,max}$ . A calibration sequence should be performed by the DRAM controller to adjust  $V_{REFDQ}$  and optimize the timing and voltage margin of the DRAM data input receivers.

# **V**<sub>REFDO</sub> Specification

Linkage

| Parameter                                   | Symbol                   | Min     | Тур   | Мах    | Unit             | Notes     |

|---------------------------------------------|--------------------------|---------|-------|--------|------------------|-----------|

| Range 1 V <sub>REFDQ</sub> operating points | V <sub>REFDQ</sub> R1    | 60%     | -     | 92%    | V <sub>DDQ</sub> | 1, 2      |

| Range 2 V <sub>REFDQ</sub> operating points | V <sub>REFDQ</sub> R2    | 45%     | -     | 77%    | V <sub>DDQ</sub> | 1, 2      |

| V <sub>REF</sub> step size                  | V <sub>REF,step</sub>    | 0.5%    | 0.65% | 0.8%   | V <sub>DDQ</sub> | 3         |

| V <sub>REF</sub> set tolerance              | V <sub>REF,set_tol</sub> | -1.625% | 0%    | 1.625% | V <sub>DDQ</sub> | 4, 5, 6   |

|                                             |                          | -0.15%  | 0%    | 0.15%  | V <sub>DDQ</sub> | 4, 7, 8   |

| V <sub>REF</sub> step time                  | V <sub>REF,time</sub>    | -       | -     | 150    | ns               | 9, 10, 11 |

| V <sub>REF</sub> valid tolerance            | $V_{REF_val_tol}$        | -0.15%  | 0%    | 0.15%  | V <sub>DDQ</sub> | 12        |

Notes: 1. V<sub>REF(DC)</sub> voltage is referenced to V<sub>DDQ(DC)</sub>. V<sub>DDQ(DC)</sub> is 1.2V.

- 2. DRAM range 1 or range 2 is set by the MRS6[6]6.

- 3.  $V_{REF}$  step size increment/decrement range.  $V_{REF}$  at DC level.

- 4.  $V_{REF,new} = V_{REF,old} \pm n \times V_{REF,step}$ ; n = number of steps. If increment, use "+," if decrement, use "-."

- 5. For n >4, the minimum value of  $V_{REF}$  setting tolerance =  $V_{REF,new}$  1.625% ×  $V_{DDQ}$ . The maximum value of  $V_{REF}$  setting tolerance =  $V_{REF,new}$  + 1.625% ×  $V_{DDQ}$ .

- Measured by recording the MIN and MAX values of the V<sub>REF</sub> output over the range, drawing a straight line between those points, and comparing all other V<sub>REF</sub> output settings to that line.

- 7. For n ≤4, the minimum value of V<sub>REF</sub> setting tolerance =  $V_{REF,new} 0.15\% \times V_{DDQ}$ . The maximum value of V<sub>REF</sub> setting tolerance =  $V_{REF,new} + 0.15\% \times V_{DDQ}$ .

- 8. Measured by recording the MIN and MAX values of the  $V_{REF}$  output across four consecutive steps (n = 4), drawing a straight line between those points, and comparing all  $V_{REF}$  output settings to that line.

- 9. Time from MRS command to increment or decrement one step size for V<sub>REF</sub>.

- 10. Time from MRS command to increment or decrement more than one step size up to the full range of V<sub>REF</sub>.

- 11. If the V<sub>REF</sub> monitor is enabled, V<sub>REF</sub> must be derated by +10ns if DQ bus load is 0pF and an additional +15 ns/pF of DQ bus loading.

- 12. Only applicable for DRAM component-level test/characterization purposes. Not applicable for normal mode of operation. V<sub>REF</sub> valid qualifies the step times, which will be characterized at the component level.

# **V<sub>REFDQ</sub> Ranges**

$\label{eq:ReFDQ} MR6[6] \mbox{ selects range 1 (60\% to 92.5\% of V_{DDQ}) or range 2 (45\% to 77.5\% of V_{DDQ}), and MR6[5:0] \mbox{ sets the } V_{REFDQ} \mbox{ level}, as listed in the following table. The values in MR6[6:0] will update the V_{DDQ} range and \mbox{ level} independent of MR6[7] \mbox{ settings}. It is recommended MR6[7] \mbox{ be enabled when changing the settings} in MR6[6:0], and it is highly recommended MR6[7] \mbox{ be enabled when changing the settings in MR6[6:0]} multiple times during a calibration routine.}$

# V<sub>REFDQ</sub> Range and Levels

| MR6[5:0] | MR6[6] 0 =<br>Range 1 | MR6[6] 1 =<br>Range 2 | MR6[5:0] | MR6[6] 0 =<br>Range 1  | MR6[6] 1 =<br>Range 2 |  |  |

|----------|-----------------------|-----------------------|----------|------------------------|-----------------------|--|--|

| 00 0000  | 60.00%                | 45.00%                | 01 1010  | 76.90%                 | 61.90%                |  |  |

| 00 0001  | 60.65%                | 45.65%                | 01 1011  | 77.55%                 | 62.55%                |  |  |

| 00 0010  | 61.30%                | 46.30%                | 01 1100  | 78.20%                 | 63.20%                |  |  |

| 00 0011  | 61.95%                | 46.95%                | 01 1101  | 78.85%                 | 63.85%                |  |  |

| 00 0100  | 62.60%                | 47.60%                | 01 1110  | 79.50%                 | 64.50%                |  |  |

| 00 0101  | 63.25%                | 48.25%                | 01 1111  | 80.15%                 | 65.15%                |  |  |

| 00 0110  | 63.90%                | 48.90%                | 10 0000  | 80.80%                 | 65.80%                |  |  |

| 00 0111  | 64.55%                | 49.55%                | 10 0001  | 81.45%                 | 66.45%                |  |  |

| 00 1000  | 65.20%                | 50.20%                | 10 0010  | 82.10%                 | 67.10%                |  |  |

| 00 1001  | 65.85%                | 50.85%                | 10 0011  | 82.75%                 | 67.75%                |  |  |

| 00 1010  | 66.50%                | 51.50%                | 10 0100  | 83.40%                 | 68.40%                |  |  |

| 00 1011  | 67.15%                | 52.15%                | 10 0101  | 84.05%                 | 69.05%                |  |  |

| 00 1100  | 67.80%                | 52.80%                | 10 0110  | 84.70%                 | 69.70%                |  |  |

| 00 1101  | 68.45%                | 53.45%                | 10 0111  | 85.35%                 | 70.35%                |  |  |

| 00 1110  | 69.10%                | 54.10%                | 10 1000  | 86.00%                 | 71.00%                |  |  |

| 00 1111  | 69.75%                | 54.75%                | 10 1001  | 86.65%                 | 71.65%                |  |  |

| 01 0000  | 70.40%                | 55.40%                | 10 1010  | 87.30%                 | 72.30%                |  |  |

| 01 0001  | 71.05%                | 56.05%                | 10 1011  | 87.95%                 | 72.95%                |  |  |

| 01 0010  | 71.70%                | 56.70%                | 10 1100  | 88.60%                 | 73.60%                |  |  |

| 01 0011  | 72.35%                | 57.35%                | 10 1101  | 89.25%                 | 74.25%                |  |  |

| 01 0100  | 73.00%                | 58.00%                | 10 1110  | 89.90%                 | 74.90%                |  |  |

| 01 0101  | 73.65%                | 58.65%                | 10 1111  | 90.55%                 | 75.55%                |  |  |

| 01 0110  | 74.30%                | 59.30%                | 11 0000  | 91.20%                 | 76.20%                |  |  |

| 01 0111  | 74.95%                | 59.95%                | 11 0001  | 91.85%                 | 76.85%                |  |  |

| 01 1000  | 75.60%                | 60.60%                | 11 0010  | 92.50%                 | 77.50%                |  |  |

| 01 1001  | 76.25%                | 61.25%                |          | 11 0011 to 11 1111 are | reserved              |  |  |

# **Speed Bin Tables**

DDR4 DRAM timing is primarily covered by two types of tables: the Speed Bin tables in this section and the tables found in the Electrical Characteristics and AC Timing Parameters section. The timing parameter tables define the applicable timing specifications based on the speed rating. The Speed Bin tables on the following pages list the <sup>t</sup>AA, <sup>t</sup>RCD, <sup>t</sup>RP, <sup>t</sup>RAS, and <sup>t</sup>RC limits of a given speed mark and are applicable to the CL settings in the lower half of the table provided they are applied in the correct clock range, which is noted.

# **Backward Compatibility**

Although the speed bin tables list the slower data rates, <sup>t</sup>AA, CL, and CWL, it is difficult to determine whether a faster speed bin supports all of the <sup>t</sup>AA, CL, and CWL combinations across all the data rates of a slower speed bin. To assist in this process, please refer to the Backward Compatibility table.

# Electrical Characteristics and AC Timing Parameters: DDR4-1600 through DDR4-2400

| Parameter                                                       |               |                                                                                                                                 | DDR4-1600 |              | DDR4-1866 |      | DDR4-2133 |      | DDR4-2400 |      |                          |         |

|-----------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-----------|------|-----------|------|-----------|------|--------------------------|---------|

|                                                                 |               | Symbol                                                                                                                          | Min       | Мах          | Min       | Мах  | Min       | Мах  | Min       | Max  | Unit                     | Notes   |

|                                                                 |               |                                                                                                                                 |           | Clock Timing |           |      |           |      |           |      |                          |         |

| Clock period average (DLL o                                     | ff mode)      | <sup>t</sup> CK (AVG,<br>DLL_OFF)                                                                                               | 8         | 20           | 8         | 20   | 8         | 20   | 8         | 20   | ns                       |         |

| Clock period average                                            |               | <sup>t</sup> CK (AVG,<br>DLL_ON)                                                                                                | 1.25      | 1.9          | 1.071     | 1.9  | 0.937     | 1.9  | 0.833     | 1.9  | ns                       | 3 , 13  |

| High pulse width average                                        |               | <sup>t</sup> CH (AVG)                                                                                                           | 0.48      | 0.52         | 0.48      | 0.52 | 0.48      | 0.52 | 0.48      | 0.52 | <sup>t</sup> CK<br>(AVG) |         |

| Low pulse width average                                         |               | <sup>t</sup> CL (AVG)                                                                                                           | 0.48      | 0.52         | 0.48      | 0.52 | 0.48      | 0.52 | 0.48      | 0.52 | <sup>t</sup> CK<br>(AVG) |         |

| Clock period jitter                                             | Total         | <sup>t</sup> JITper_tot                                                                                                         | -63       | 63           | -54       | 54   | -47       | 47   | -42       | 42   | ps                       | 17 , 18 |

|                                                                 | Deterministic | <sup>t</sup> JITper_dj                                                                                                          | -31       | 31           | -27       | 27   | -23       | 23   | -21       | 21   | ps                       | 17      |

|                                                                 | DLL locking   | <sup>t</sup> JITper,lck                                                                                                         | -50       | 50           | -43       | 43   | -38       | 38   | -33       | 33   | ps                       |         |

| Clock absolute period <sup>t</sup> CK (ABS)                     |               | MIN = <sup>t</sup> CK (AVG) MIN + <sup>t</sup> JITper_tot MIN; MAX = <sup>t</sup> CK (AVG) MAX +<br><sup>t</sup> JITper_tot MAX |           |              |           |      |           |      | ps        |      |                          |         |

| Clock absolute high pulse width<br>(includes duty cycle jitter) |               | <sup>t</sup> CH (ABS)                                                                                                           | 0.45      | -            | 0.45      | _    | 0.45      | _    | 0.45      | _    | <sup>t</sup> CK<br>(AVG) |         |

| Clock absolute low pulse width<br>(includes duty cycle jitter)  |               | <sup>t</sup> CL (ABS)                                                                                                           | 0.45      | -            | 0.45      | _    | 0.45      | _    | 0.45      | _    | <sup>t</sup> CK<br>(AVG) |         |

| Cycle-to-cycle jitter                                           | Total         | <sup>t</sup> JITcc _tot                                                                                                         | -         | 125          | _         | 107  | -         | 94   | -         | 83   | ps                       |         |